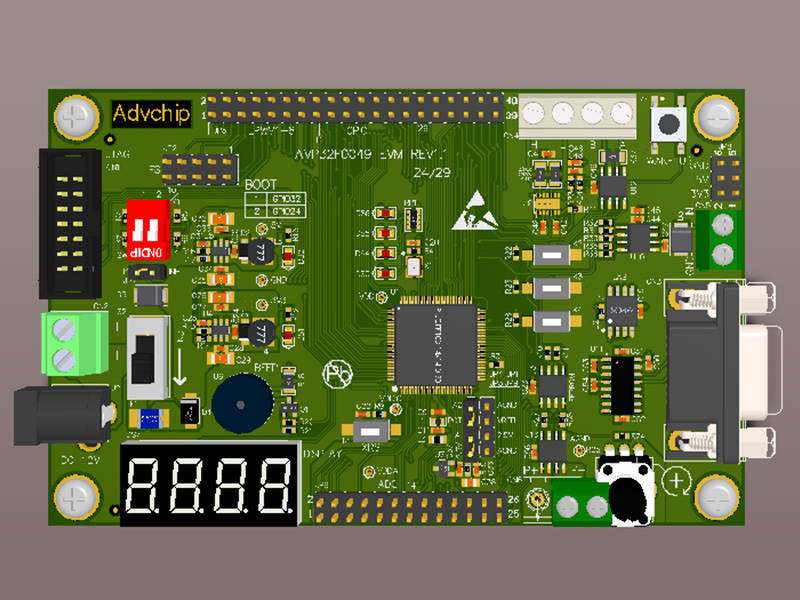

AVP32F0049

AVP32F0049 is a high-performance floating-point processor with a Harvard bus architecture and a clock speed of up to 120MHz; Supports up to 256KB (128KW) of flash memory and three independent 12 bit ADCs; Contains advanced control peripherals (with frequency independent ePWM/HRPWM and eCAP); Supports connections through various industry standard communication ports such as SPI, SCI, I2C, LIN, and CAN.

Datasheet →industry Automotive Standard

• AVP32F0049 32 bits CPU

- Main frequency 120MHz

- IEEE 754 Single Precision Floating Point Unit (FPU)

- trigonometric functions mathematical units (TMUs)

• Compared with software library methods, the common trigonometric functions include 3 times to 4 times cycle Performance improvement

• 13 Periodic Pike transform

- Viterbi/ complex mathematical unit (VCU-I)

- Ten hardware breakpoints (including ERAD )

• Programmable Control Law Accelerator (CLA)

- 120 MHz

- IEEE 754 single precision floating-point instructions

- is independent of the main CPU and executes code

• on-chip memory

- provides 256KB (128KW) flash memory (}) on two independent storage banks ECC Protection)

- 100KB (50KW) RAM( ECC protection or parity protection)

- Supports third-party development for dual zone security

- Identification (UID) Number

• Clock and system control

- Two internal zero pins 10MHz oscillators

- on-chip crystal oscillator and external clock input

- windowed watchdog timer module

- Clock loss detection circuit

• 1.1 V kernel 3.3V I/O Design

- can generate 1.1 V Internal voltage of VREG or DC-DC allows for single power supply design

- undervoltage reset (BOR) circuit

• system peripherals

- 6 channels direct memory access (DMA) controllers

- 40 independent programmable multiplexed general-purpose inputs / outputs (GPIO) pins

- provides 21 digital inputs on the analog pins

- Enhanced Peripheral Interrupt Extension (ePIE) Module

- supports multiple low-power modes with external wake-up function (LPM)

- Embedded real-time analysis and diagnosis (ERAD)

• Communication peripherals

- A power management bus (PMBus) interface

- One Integrated Circuit Bus (I2C) Interface(Pin Bootable)

- Two Controller Area Network (CAN) Bus Ports (Pin Bootable)

- Two serial peripheral interfaces (SPI) ports (pin bootable)

- Two serial communication interfaces compatible with UART (SCI)

(pin bootable)

- A local interconnect network compatible with UART (LIN)

- A fast serial interface with transmitter and receiver (FSI)

• simulation system

- Three 3.45MSPS 12 bit analog-to-digital converters (ADC)

• Up to 21 external channels

• Each ADC has four integrated post-processing blocks . tag11 (PPB)

- Seven window comparators with 12 bit reference digital to analog converters (DAC) (CMPSS)

• digital interference filters

- Two 12 bit buffers DAC outputs

- Seven programmable gain amplifiers (PGA)

• Programmable gain settings: 3 、 6 、 12 、 24

• Programmable output filtering

• Enhanced control peripheral

- 16 with high-resolution functionality () 150ps resolution) of ePWM channels

• have high-resolution integrated dead zone support

• integrated hardware bounce zone (TZ)

- Seven enhanced capture (eCAP) modules

• provide high-resolution capture (HRCAP)

on two modules - Two enhanced orthogonal encoder pulses (eQEP) modules

that support CW/CCW operation modes - Four ∑ - Δ Filter Module (SDFM) Input Channel (Two Parallel Filters per Channel)

• Standard SDFM Data Filtering

• A comparator filter

• configurable logic block (CLB)

for fast operation in cases of overestimation or underestimation - Enhance existing peripheral functionality

- supports location manager solutions

• Encapsulation Options:

- 100 Pin Thin Quad Flat Package (LQFP)

- 64 pins thin square flat package () LQFP )

- 56 pin ultra-thin leadless square flat package (VQFN)

• Temperature options:

- S: -40 ° C to 125 ° C

- Q : -40 ° C to 125 ° C ( passes through ) AEC-Q100 Authentication )

CN

CN

EN

EN