ADP32F03x

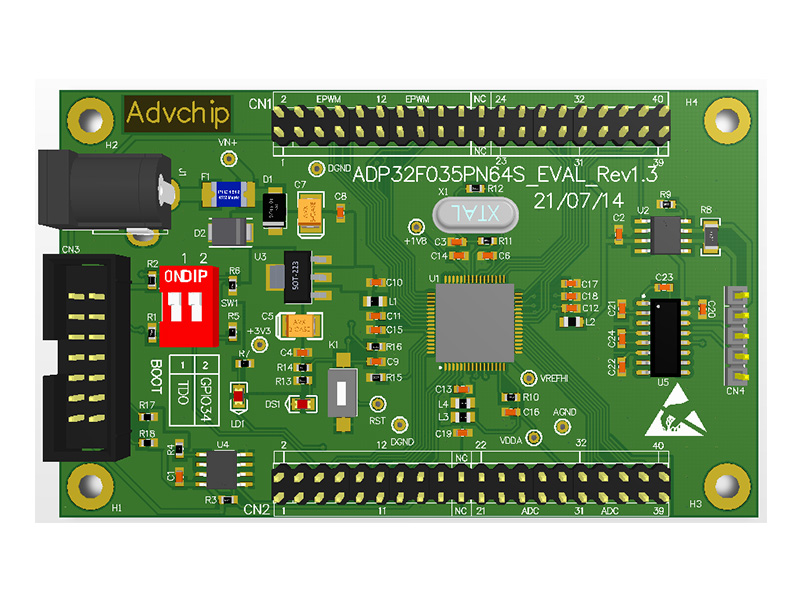

ADP32F03X is a 32-bit fixed-point digital signal processor, in which ADP32F035 supports CLA for single precision floating-point operations. The main frequency supports 60MHz, and it integrates multiple types of memory, enhanced peripherals, communication interface peripherals, and analog peripherals. It supports various types of packaging such as QFP80, QFP64, QFP56, QFP48, and QFP32. The chip has passed AEC-Q100 vehicle specification certification and can be widely used in industrial motor drives, photovoltaic inverters and digital power supplies, electric vehicles and transportation, motor control, as well as sensing and signal processing.

Datasheet →industry Automotive Standard

-32-bit central processing unit (CPU) (ADP32Fx core)

- Main frequency 60MHz (cycle 16.67ns)

-3.3V single power supply

- Integrated power on and undervoltage reset source

- on-chip flash memory, SRAM, OTP memory

- Code security module

- Serial port peripheral (SCI/SPI/I2C/LIN/eCAN)

- Enhanced control peripheral

▷ Enhanced pulse width modulator (ePWM)

▷ High resolution PWM (HRPWM)

▷ Enhanced Capture (eCAP)

▷ High Resolution Input Capture (HRCAP)

▷ Enhanced Orthogonal Encoder Pulse (eQEP)

▷ Analog to Digital Converter (ADC)

▷ on-chip temperature sensor

▷ comparator

● 32-bit Central Processing Unit (CPU) (ADP32Fx)

-60MHz (16.67ns cycle time) tag11

-16 x 16 and 32 x 32 multiply accumulate (MAC) operations

-16 x 16 dual MAC

- Harvard bus architecture

- Linkage operations

- Fast interrupt response and processing

- Unified memory programming model

- Code (using C/C++and assembly language)

The sentence is: ● Programmable Control Law Accelerator (CLA)

-32-bit floating-point arithmetic accelerator

- code execution independent of the main CPU

tag11}

- Integrated power on reset and undervoltage reset

- Low power consumption

- No analog support pins

● Clock and system control

- Two internal zero pin oscillators

- On-chip oscillator/external clock input

- supports dynamic phase-locked loop (PLL) ratio variation

- lost clock detection circuit

● Up to 45 individually programmable multiplexed GPIO

with input filtering function ● Peripheral Interrupt Extension (PIE) module

that supports all peripheral interrupts ● Three 32-bit CPU timers

● Each ePWM module contains an independent 16 bit timer

● On chip memory

- flash memory, SRAM,OTP, Boot ROM available

● 128 bit secure key/lock

- protects secure memory block

- prevents hardware reverse engineering

● serial port peripherals

- one SCI (UART) module

- two SPI modules

- one internal integrated circuit (I2C) bus 11}

- A Local Interconnect Network (LIN) bus

- An Enhanced Controller Area Network (eCAN) bus

● Simulation features

- Analysis and breakpoint functionality

● Packaging options:

-56 Pin Ultra Small Square Flat No Pin (VQFN) Package

-64 Pin Thin Square Flat (LQFP) Package

-80 Pin Thin Square Flat (LQFP) Package

-48 Pin Thin Square Flat (LQFP) Package

-32 Pin Ultra Small Square Flat No Pin (VQFN) Package

CN

CN

EN

EN